Ming Hsieh Department of Electrical Engineering

# Wideband Frequency Synthesis with Rapid Frequency Hopping

**Sushil Subramanian and Hossein Hashemi** Ming Hsieh Department of Electrical Engineering

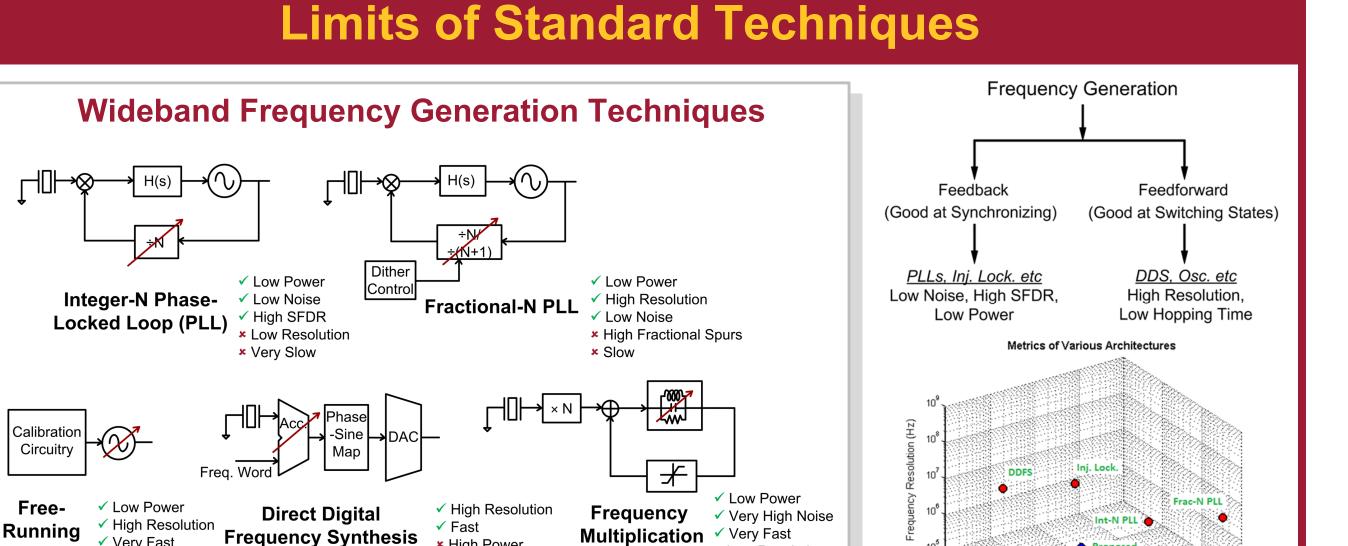

✓ Very Fast

Oscillator × Very High Noise

# **Motivation**

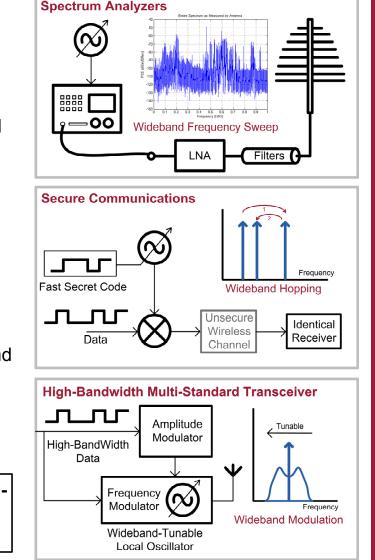

#### **Conventional Spectral Analysis: Spectrum Analyzers** $\bigotimes$ • The sweep rate of synthesizer based spectrum analyzers is limited to the acquisition and tracking of phase-locked loops (PLLs). γ---00 Direct digitization and FFT requires high-speed data converters that consume a lot of power. **Key Applications:** Spectrum analyzer with small sweep time and real-time power measurement. $(\infty)$ ுட Secure communications over a wideband with Fast Secret Code rapidly hopping carrier frequency. Data Multi-band OFDM applications in ultra-wideband (UWB) communications. ഹഹ Multi-standard wideband downconversion with high modulation bandwidths.

Objective: Design a low power, low noise Rapid-Hopping Frequency Synthesizer with high spectral purity and frequency resolution

•

and Locking

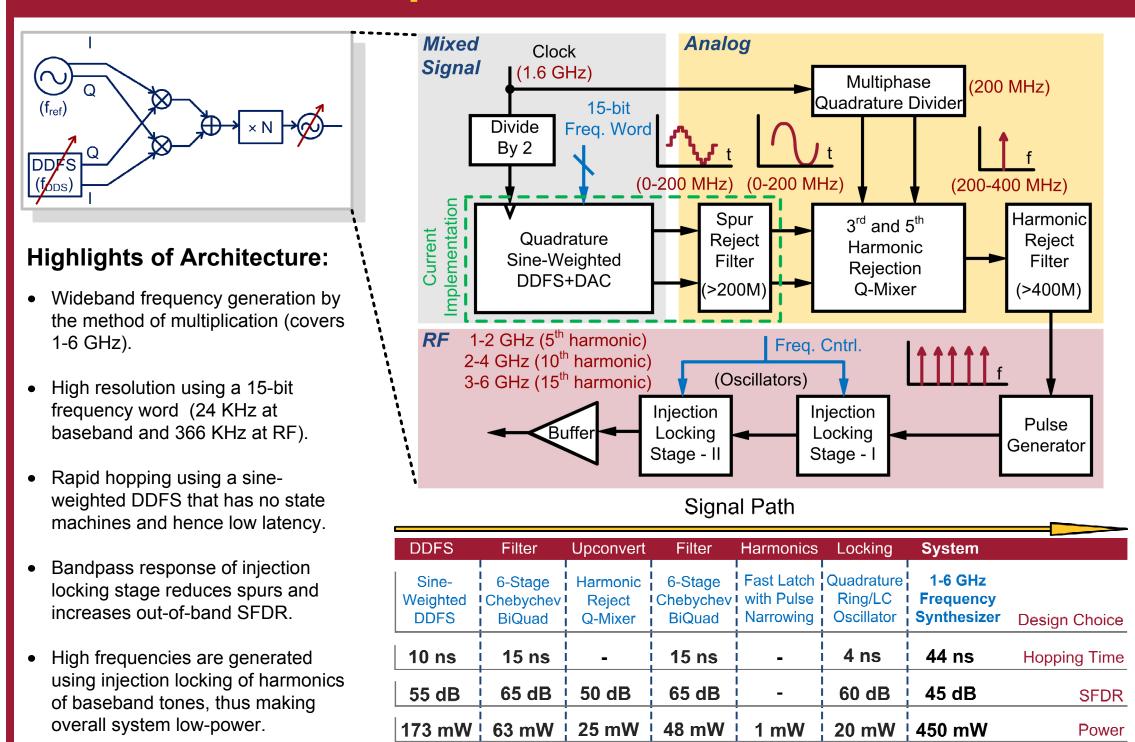

#### **Proposed Architecture**

### **General Working Principle**

Power Consumption (W

Hopping Time (s)

Low Resolution

Low SFDR

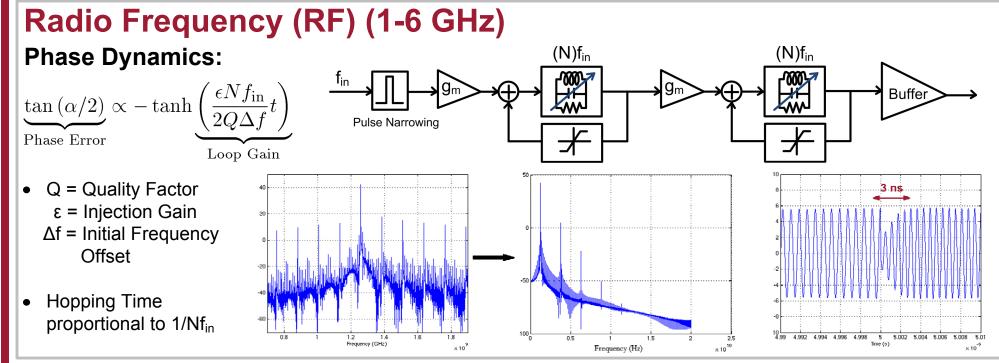

#### **Baseband (0-200 MHz)**

High Power

Low SFDR

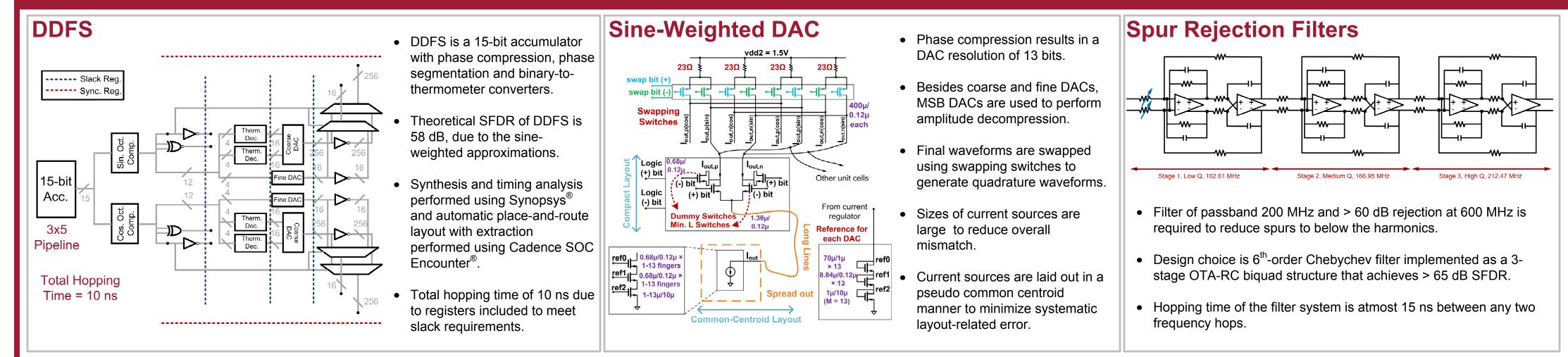

(DDFS)

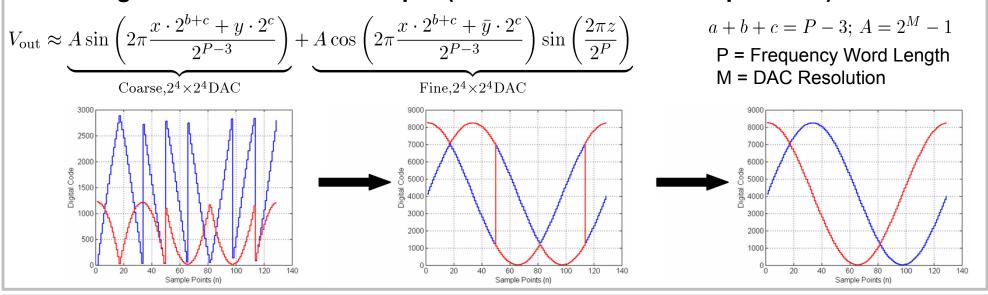

Phase Segmentation and DAC Output (after Quarter-wave Compression):

# Integrated Circuit Implementation

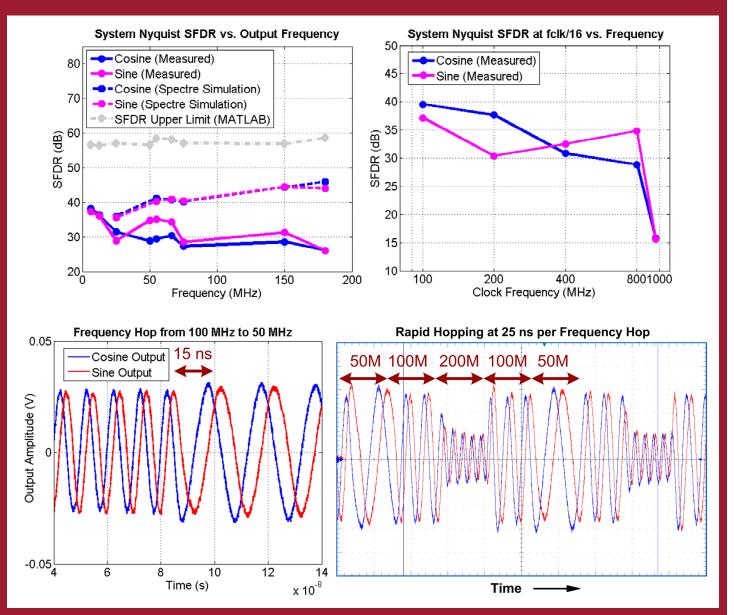

# **Measurement Results**

### **Performance Summary**

#### (Results Specified for Baseband)

| Specification                            | Achieved Result                                                    |

|------------------------------------------|--------------------------------------------------------------------|

| Process                                  | 0.13 μm CMOS                                                       |

| <b>Reference Clock</b>                   | 800 MHz                                                            |

| Frequency Range                          | 0-200 MHz                                                          |

| Frequency Resolution                     | 24.41 KHz                                                          |

| <b>DAC</b> Resolution                    | 13 bits                                                            |

| Phase Noise                              | -123 dB/Hz (at 100 KHz offset)                                     |

| Frequency Stability                      | (reference dependent)                                              |

| SFDR (Average)                           | 33 dB                                                              |

| W/(GHz × 2 <sup>SFDR/6</sup> )           | 0.0116                                                             |

| HoppingTime                              | <15 ns                                                             |

| Power Consumption (at highest frequency) | V <sub>dd</sub> = 1.2 V, 180 mW<br>V <sub>dd</sub> = 1.5 V, 240 mW |

| Chip Area                                | 7.51 mm <sup>2</sup> (including pads)                              |

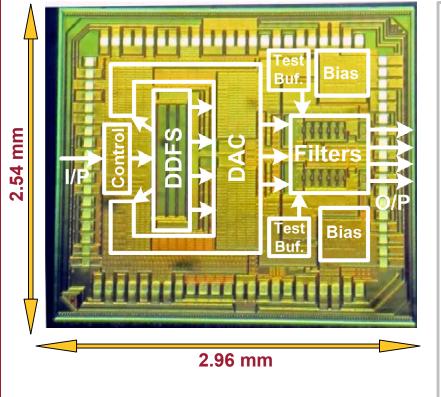

# **Chip Photograph and Conclusions**

- 1-6 GHz rapid-hopping synthesizer architecture optimized for SFDR, power consumption and frequency resolution.

- DC-200 MHz reference designed and implemented in standard CMOS.

#### **Future Work**

- Design of complete system and possible use in existing software defined radio (SDR) applications.

- Enabling high-bandwidth modulation and secure transceivers using custom, fast digital control circuits.

- Frequency synthesizers are important circuit blocks, however there exists a fundamental control theoretic tradeoff between quality of synchronization and bandwidth. Studying this tradeoff in-depth is valuable and enables interesting applications in RF circuits.

- S. Subramanian and H. Hashemi, *IEEE IMS 2013*, [submitted]

#### January 2013

#### Contact: Sushil Subramanian, sushilsu@usc.edu