# A VARIATION AWARE RESILIENT FRAMEWORK FOR POST-SILICON DELAY VALIDATION OF HIGH PERFORMANCE CIRCUITS

## Prasanjeet Das Prof. Sandeep Gupta (Advisor)

February 6, 2013

This research was sponsored by Intel Corporation

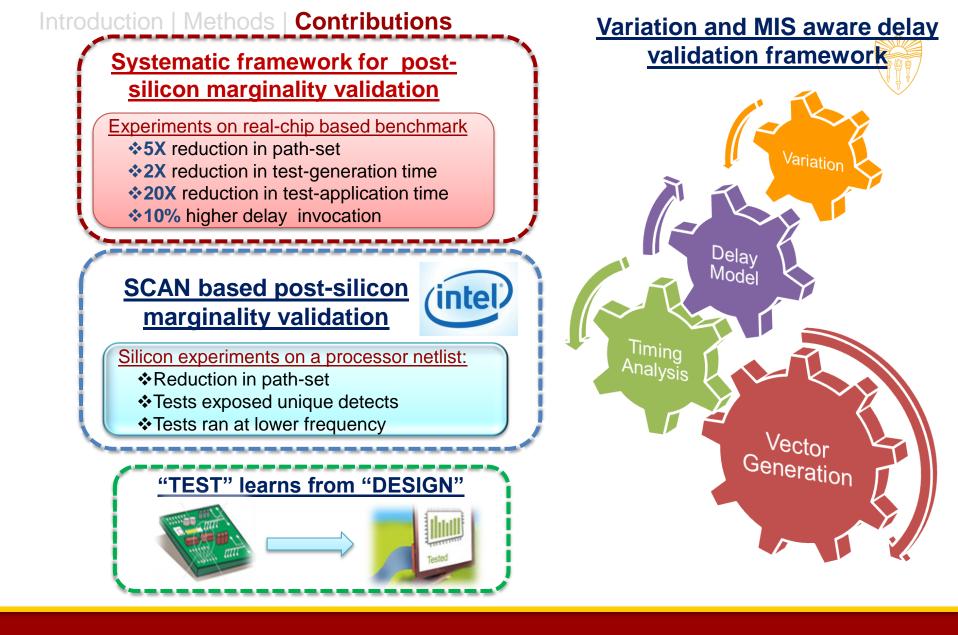

Introduction | Methods | Contributions

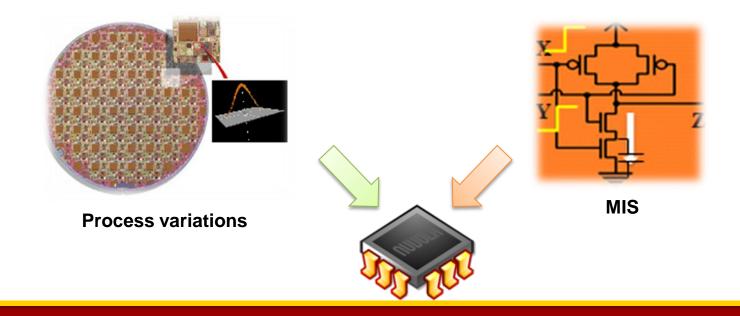

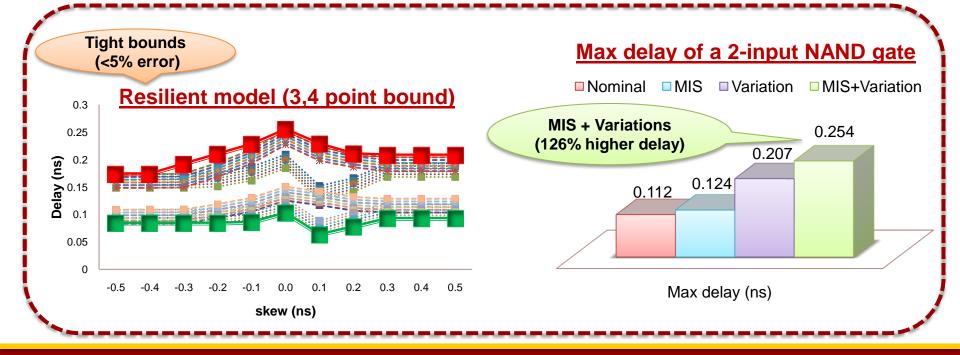

Delay measured on fabricated chips tend to deviate from estimated nominal delay due to

### Multiple input switching (MIS)

✤ Increase/decrease of delay due to lower order effects.

### Normal process variations

Delay marginalities due to lack of precise fabrication control.

Within scope hard to detect

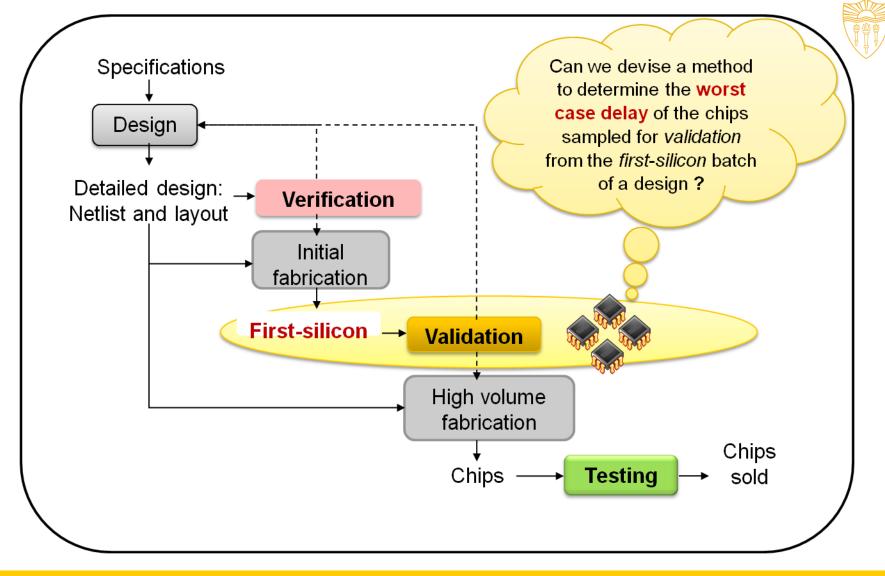

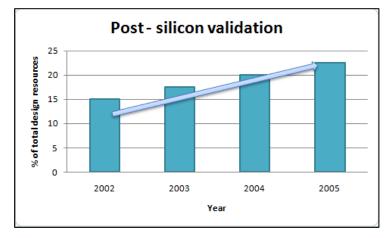

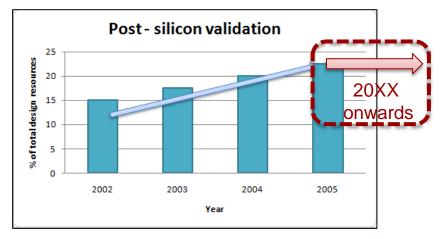

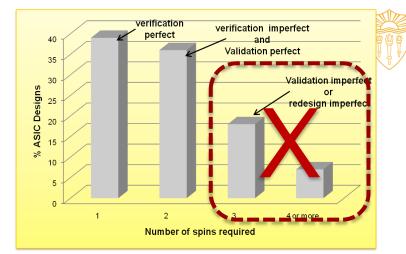

### Increasing importance of validation

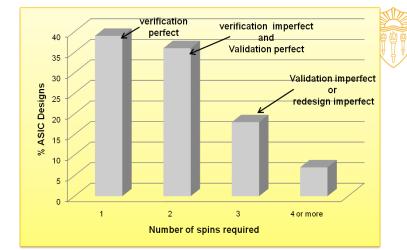

#### **Current validation approaches inadequate**

### Current delay-testing approaches inadequate

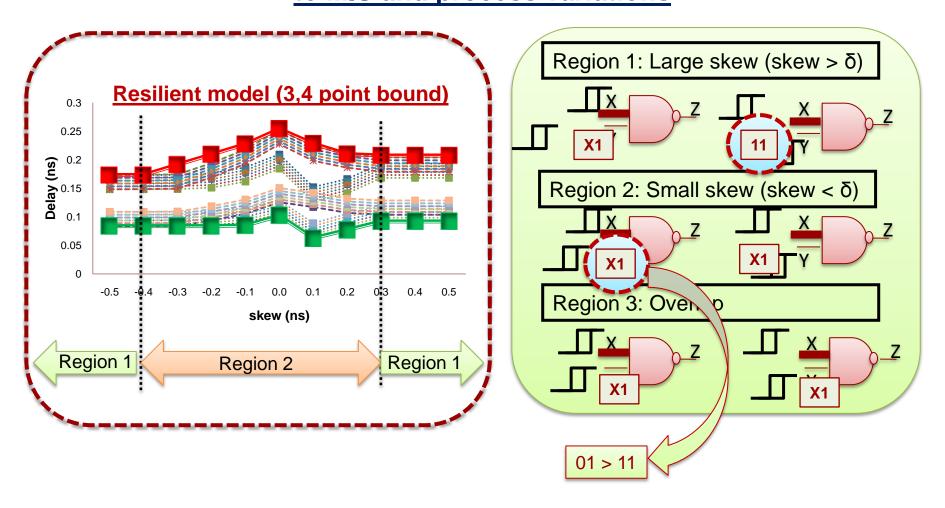

# Bounding approximations to capture variations and MIS using bounds at low complexities.

#### This model captures

- ✓ Input slew

- ✓ Input position

- ✓ Output load.

- ✓ Input skew (MIS)

- ✓ State of internal capacitances

- ✓ Process variations

# **Resilient delay model**

PrasanjeetDas@USC2013

/iterbi

School of Engineering

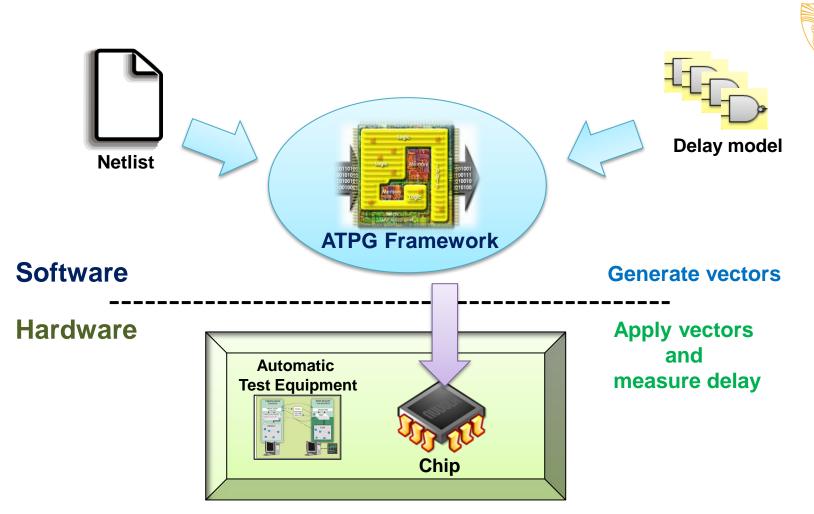

# Generate vectors that can account for delay increase due to MIS and process variations

# MIS-aware vector

generator

PrasanjeetDas@USC2013

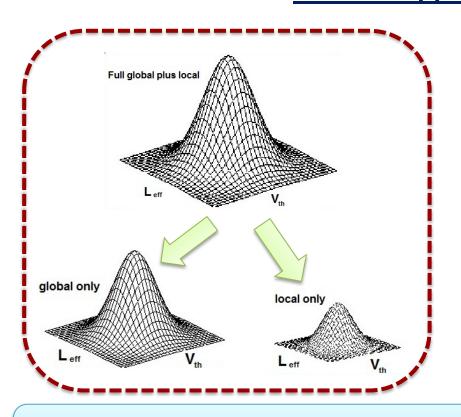

### Segment global process variation envelope to reduce test-volume and test application time

Divide and conquer

Application

0.025

0.107

0.025

0.107

0.466

0.107

Global-only process shift can be estimated using ring-oscillator based process monitors.

SC Viterbi School of Engineering

#### PrasanjeetDas@USC2013

University of Southern California

**Probability**

0.025

0.107

0.025

PrasanjeetDas@USC2013

# **Short term benefits**

Increasing importance of validation

#### **Current** validation approaches inadequate

**Current** delay-testing approaches inadequate

Long term benefits

University of Southern California **10**

PrasanjeetDas@USC2013